JSTAR Software Digital Twins

“Fail Virtually, Succeed Actually”

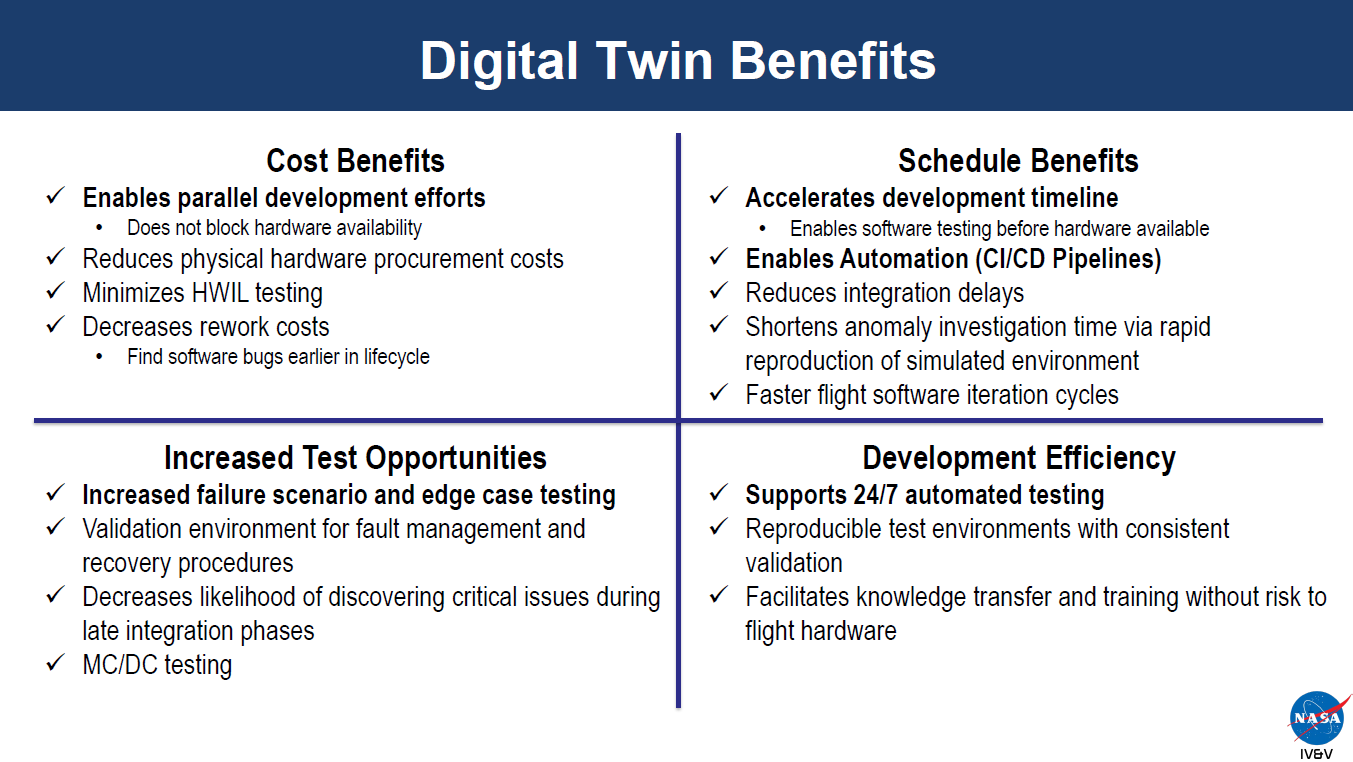

Value Proposition: Our hardware emulation digital twin technology transforms spacecraft/system development through an all-software solution that accelerates timelines, expands testing capabilities, and reduces costs—without physical hardware constraints.

Key Benefits

Using Digital Twin approach on an in-house satellite mission resulted in validated flight software completion prior to environmental testing.

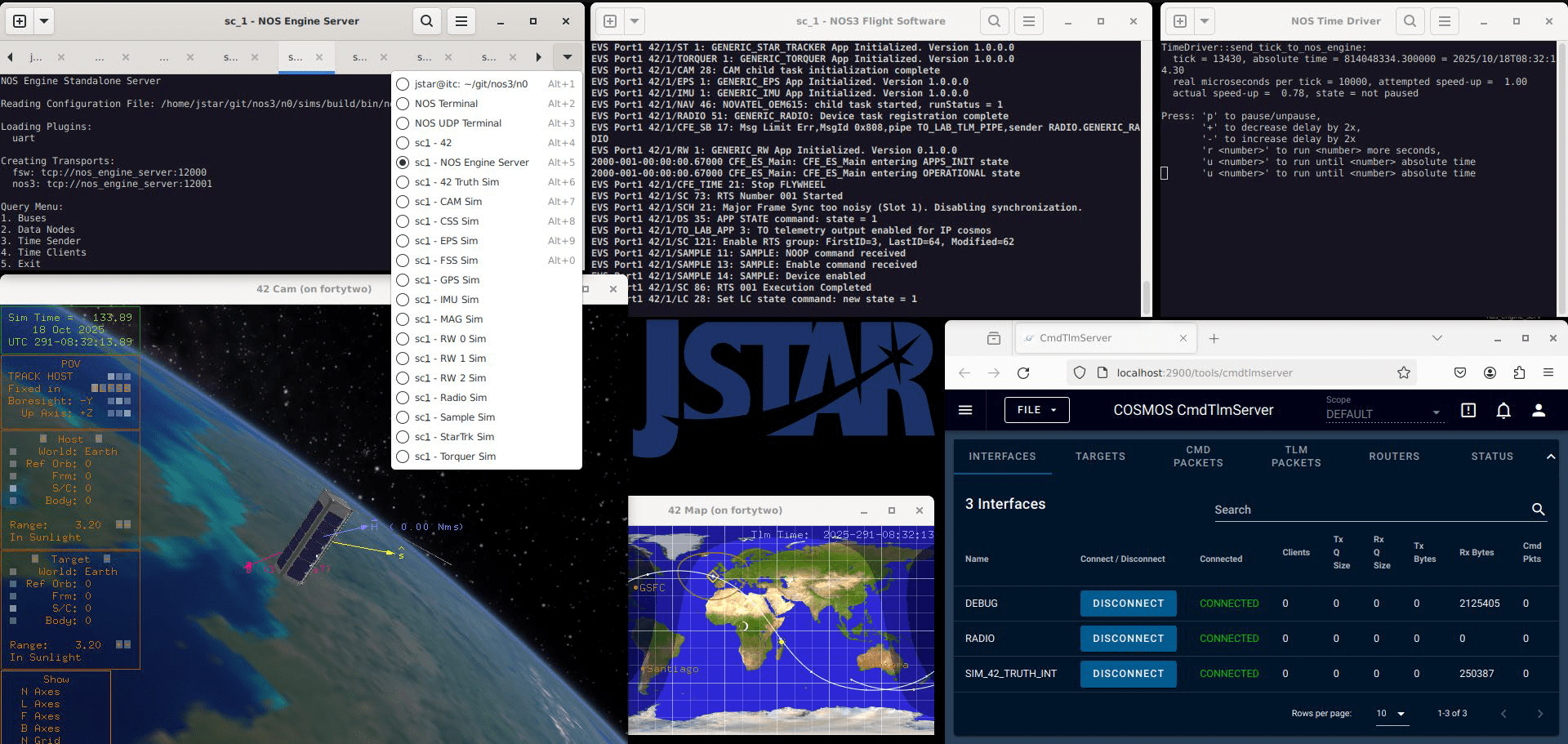

Our Approach

Hardware Emulation

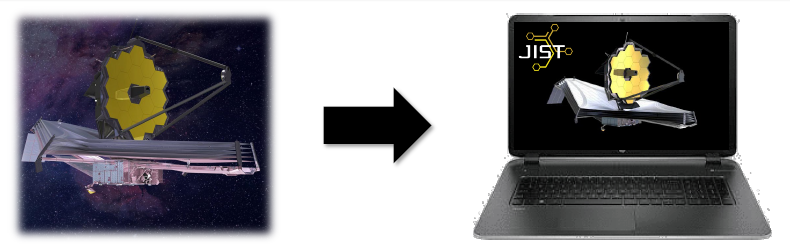

Condense an entire flight system to a laptop or cloud solution.

- Flight computer hardware is emulated

- Sensors/actuators are simulated

- Flight software binaries executed as delivered

- Ground operations software integrated as-is

Benefits

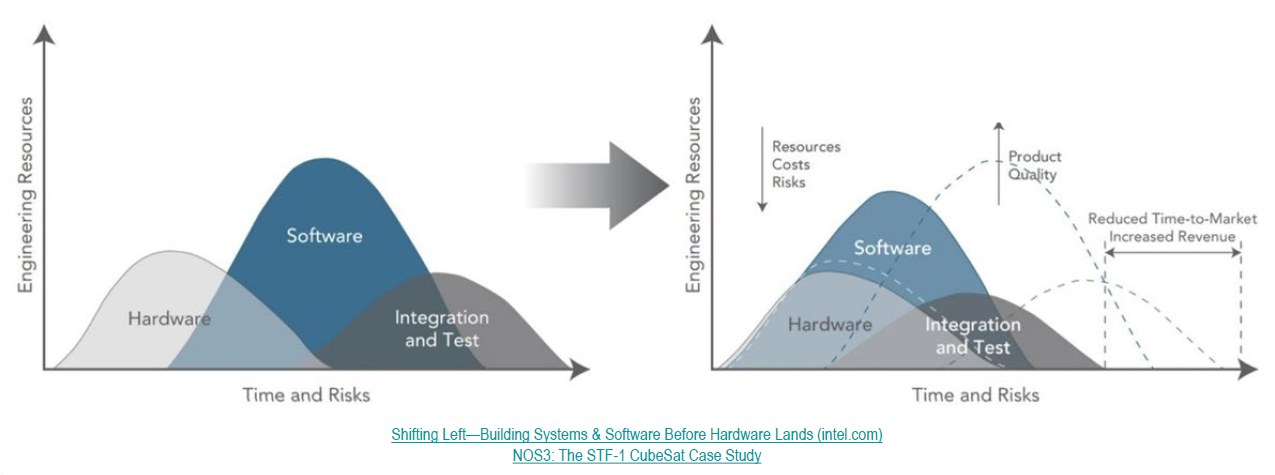

Digital Twins shift the traditional software development cycle.

Digital Twins greatly increase test resources.

JSTAR – A Software Digital Twin Factory

| Mission | Platform |

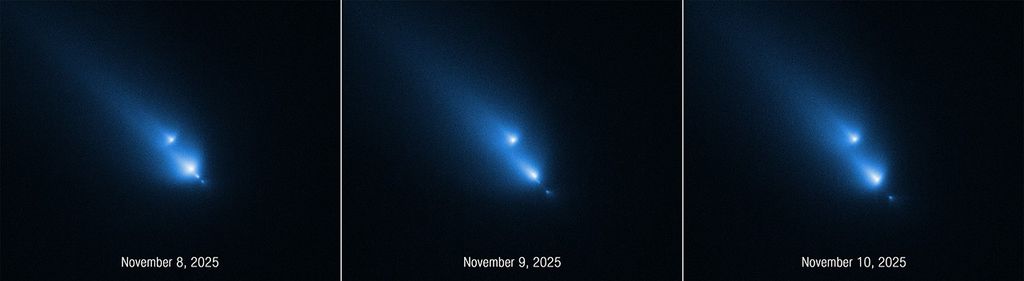

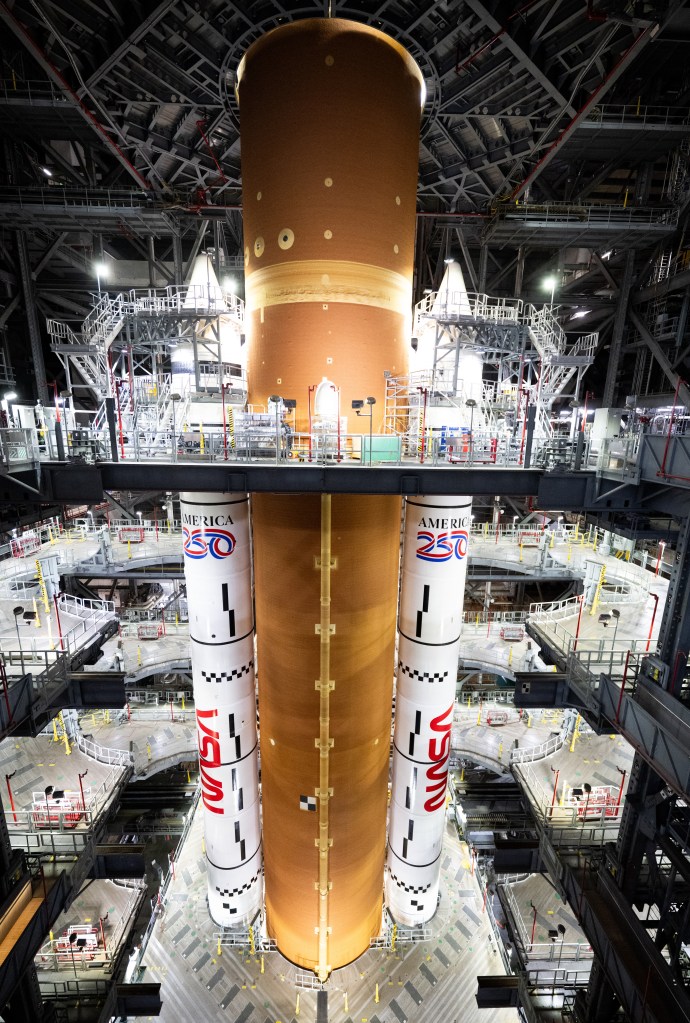

| Integrated Tri-Program Simulation (SLS, MPCV, EGS) | Advanced Risk Reduction Integrated Simulation and Test Lightweight Environment (ARRISTOTLE) |

| Roman Space Telescope | WISP, RST Digital Twin |

| Europa Clipper | Europa Clipper Hardware Abstraction Operational Environment System (ECHOES) |

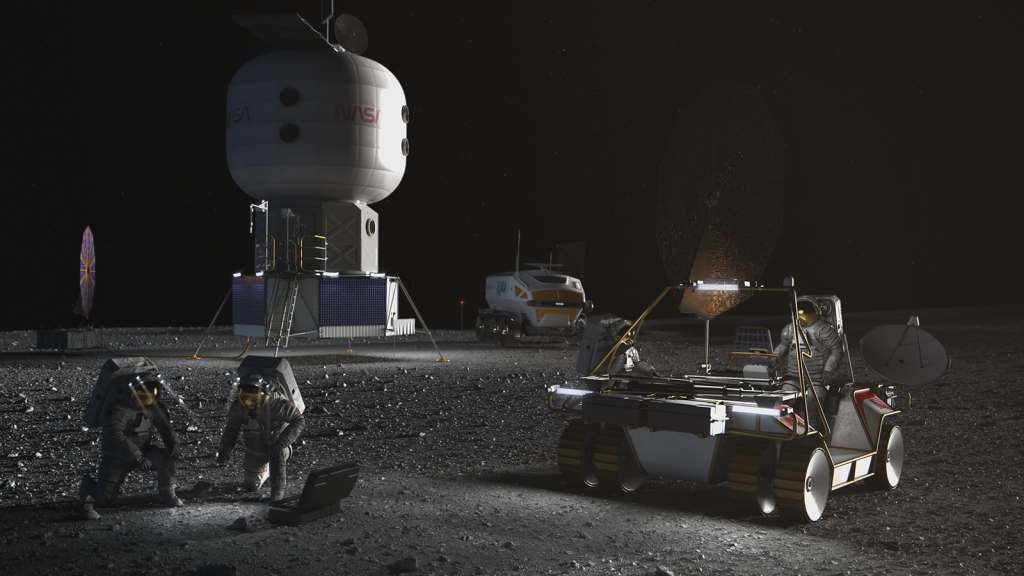

| Gateway | Gateway-in-a-Box |

| James Webb Space Telescope (JWST) | JWST Integration Simulation Test (JIST) |

| Open-Source Simulation Framework | NASA Operation Simulator for Small Satellites (NOS3) |

| Psyche | Psyche Hardware Abstraction Simulation Environment (PHASE) |

| Space Launch System | SLS Software-only Simulation (S3) |

| Multi-Purpose Crew Vehicle (MPCV) | Software-only CEV Risk Reduction Analysis and Test Engineering Simulator (SOCRRATES) |

| LM Product Line | Soft Sim |

| International Space Station | MDM Application Development Environment (MADE) |

Independent Testing Areas

| Failover fault testing | Non-deterministic memory object placement |

| GNC scenarios and faulting | EVR throttling and Overrun |

| SUROM cycling for valid FSW image | Partition Margin analysis |

| STM, DEADP, xRTI corruption | DWN overrun and repeat frames – Linked-list (0x569) mode |

| Bus faults – 1553, MBUS | SUROM Bad page detection and mapping |

| Time sync corruption | SDRAM Fault Injection |

| Fault RTI interrupt and test for FSW spacecraft reset | Identified FSW writes to read-only registers early in project |

| Impact of NULL pointer dereference | Logic errors for some EVR handling |

| PicoC and PITH error handling | FDU WDT stroking logic |

Contact Us For More Information

If you would like more information, please contact either:

- Justin Morris – Justin.R.Morris@nasa.gov