Michael Hamilton

Auburn University

LuSTR21 Overview Chart Hamilton.pdf

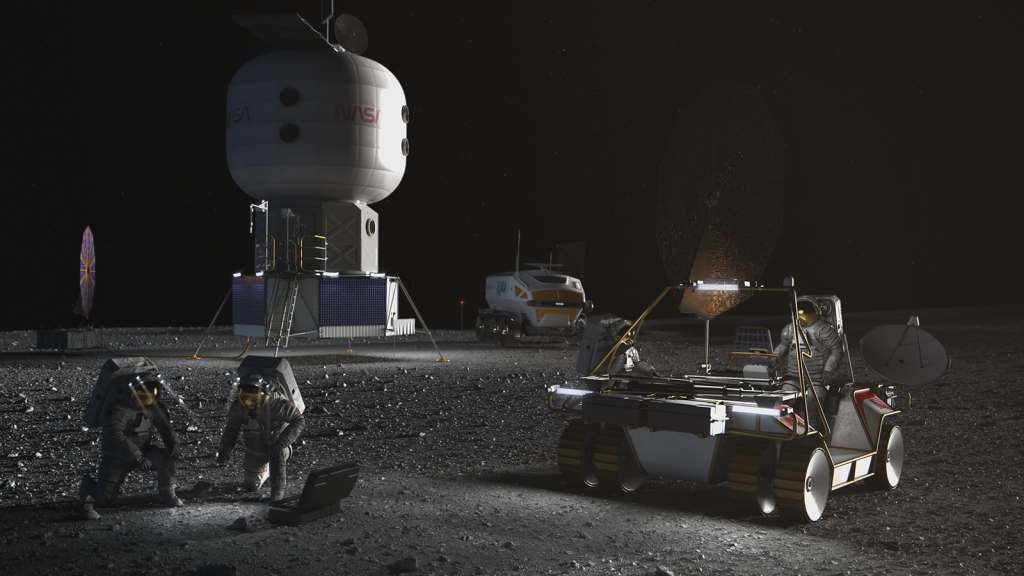

Cold-Tolerant Electronics and Packaging for Lunar Surface Exploration (CTE-PLuS) will lay the foundations for high-performance electronics for future lunar exploration missions. Cold and shadowed regions on the Moon likely contain valuable resources for lunar surface missions. The lunar surface is a challenging environment for electronics and associated packaging used in systems that will search for these substances; with a wide range of temperatures, from a low of 25 K in permanently shadowed regions (PSRs), to a high of 400 K in sunlight, along with large temperature swings. Radiation exposure, modest in terms of total ionizing dose, must be considered for tolerance to single event phenomena. Legacy approaches for robust operation through lunar night and in PSRs have required a warm electronics box (WEB) for thermal control and radiation shielding, which severely impacts system size, weight, power and cost (SWaP-C), complicates wiring, and forces mission designers into highly centralized architectures, constraining science capabilities. To be cost-effective and future-proof, electronics should be realized using commercially-available, low-cost integrated circuit (IC) technologies and standard electronics packaging that are extreme-cold-tolerant, wide temperature range and radiation capable, and highly reliable, without WEBs. The CTE-PLuS team, comprising groups from Auburn University, Georgia Tech. and University of Tennessee, will: (1) implement analog/RF/bias circuitry using 90 nm SiGe BiCMOS, (2) implement analog-to-digital converter (ADC) circuits using deeply-scaled 22 nm SOI CMOS, and (3) realize temperature-tolerant packaging approaches to provide the performance and reliability to achieve LuSTR Topic 3 goals: e.g., degradation less than 20% during 3 years at 70 K.