### **Space Hardware**

http://www.nasa.gov/centers/ivv/JSTAR/ITC.html

Steve Yokum Steve.Yokum@TMCTechnologies.com

> NASA IV&V Facility 100 University Drive Fairmont, WV 26554

- The Need for Space Hardware

- JSTAR Resources

- Use Case

# The Need for Space Hardware

**Software Capabilities**

- Software Models of Hardware have tremendous benefits:

- Functionally equivalent

- Portable/Sharable

- But still possess a few limitations:

- Timing

- Performance

- Accuracy under Anomaly and Exceptions.

OFTWA

- Timing bugs can be some of the most difficult to resolve

- May take hours/days to reproduce

- Inconsistent

- Often the result of complex interactions between multiple threads

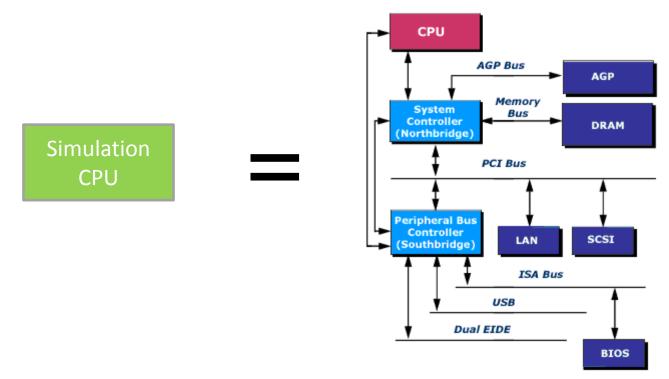

• A Software Model is limited because it must model multiple chipsets in a single CPU

- Each chipset must be given *scheduled* CPU time in the host processor.

- Asynchronous events (e.g. interrupts):

- Only generated when chip is scheduled

- Possibly arrive in a different order from hardware.

- Latency/Jitter

- Difficult to recreate exact timings between components. Software Model is virtually instant.

- The assembly instructions of each virtual chipset must be run by the host CPU for each chip in a virtual emulation.

- This can make real-time difficult to achieve

- Only matters if external components are interfaced

- Ground Station

- Dynamics Model

- Hardware

| Function          | Address    | Instruction         |

|-------------------|------------|---------------------|

| ghs_eofn_init7Exe | 0x00017050 | addi r12,r12,6084   |

| ghs_eofn_init7Exe | 0x00017054 | stw r12,12(r3)      |

| ghs_eofn_init7Exe | 0x00017058 | li r11,0            |

| ghs_eofn_init7Exe | 0x0001705c | stw r11,-32728(r13) |

| ghs_eofn_init7Exe | 0x00017060 | beqlr               |

| ghs_eofn_init7Exe | 0x00017064 | b 0xlce04           |

| ct7ExecCSCFP11Exe | 0x00017068 | stwu r1,-32(r1)     |

| ct7ExecCSCFP11Exe | 0x0001706c | stmw r27,12(r1)     |

| ct7ExecCSCFP11Exe | 0x00017070 | mr r27,r8           |

| ct7ExecCSCFP11Exe | 0x00017074 | li r9,0             |

| ct7ExecCSCFP11Exe | 0x00017078 | mflr r0             |

| ct7ExecCSCFP11Exe | 0x0001707c | stw r0,36(r1)       |

| ct7ExecCSCFP11Exe | 0x00017080 | mr r31,r3           |

| ct7ExecCSCFP11Exe | 0x00017084 | stw r9,0(r31)       |

CPU

PC

MAR

MDR

CU

**DMA** Controller

IR

Bus

Bus

Bus

General

Purpose

Registers

I/O

Inter

-face

I/O

Inter

-face

0

Bus

Device

Device

ALU

Accumula-

tor

Address

Data

Control

Memory

- Modelling hardware in software can be a tremendous undertaking

- It involves capturing:

- Interrupts

- DMA

- Registers

- Memory Maps

- Buses (PCI, VME, etc)

- Exceptions

- Interactions of multiple components

- Recreating system timings

- Some of the problems that often occur when modeling hardware:

- The hardware specification is not accurate nor complete

- Due to the complexity of the task, often the nominal paths are modeled, but the exceptions and anomalies get left out.

- Analog interfaces are free of noise

- In specialized cases, this can make recreating errors impossible.

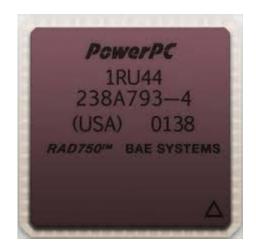

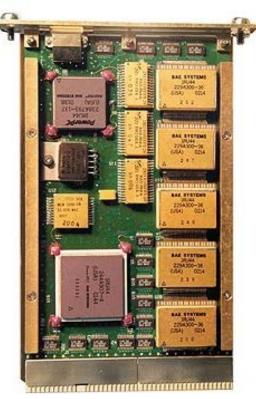

## **JSTAR Resources**

- 2 Models:

- 3U

- 128 Mb RAM

- 1553, SpaceWire, Ethernet on cPCl backplane

- 6U

- 36 Mb RAM

- Integrated 1553 and SpaceWire

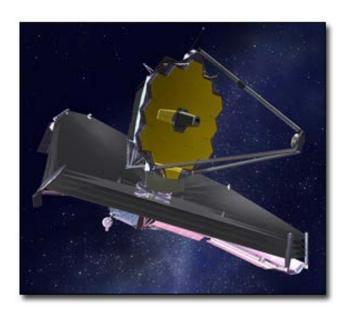

- The RAD750 is the de-facto processor for many NASA missions, including:

- Deep Impact

- Mars Reconnaissance Orbiter

- STEREO

- LRO

- SDO

- JUNO

- GPM

- JWST

**Other Resources**

- ITC has a variety of 1553 and SpaceWire test sets to simulate common space

- protocols

| Brd 2 Dev 1                     | RTO A B   | RT8 A B    | RT16 A B   | RT24 A           |

|---------------------------------|-----------|------------|------------|------------------|

| Monitor<br>SnapShot Storing     | RT1 A B   | RT9 A B    | RT17 A B   | RT25 _ A         |

| Archive                         | RT2 _ A B | RT10 A B   | RT18 _ A B | RT26 _ A         |

| Bus load 0.3                    | RT3 A B   | RT11 A B   | RT19 _ A B | RT27 _ A         |

| BC Control<br>Loop<br>Count 257 | RT4 A B   | RT12 _ A B | RT20 A B   | RT28 _ A         |

|                                 | RT5 A B   | RT13 _ A B | RT21 _ A B | RT29 _ A         |

|                                 | RT6 A B   | RT14 A B   | RT22 A B   | RT30 _ A         |

|                                 | RT7 A B   | RT15 A B   | RT23 _ A B | RT31 _ A         |

|                                 | 1         | 1          |            | 279.14:05:09:384 |

### Capabilities with hardware RAD750

- ITC can execute VxWorks and RTEMS operating systems on the RAD750 platforms

- ITC can recompile and target sections of mission code that require analysis

- ITC is currently building a 1553 and SpaceWire capability to interface with external systems including Software Models

#### • Juno Anomaly

- Juno had a condition where the processor raised an ISI exception

- Unique to this condition was that the exception kept getting raised at 10Hz instead of the task suspending

- Eventually a system monitor switched sides because the faulting task was not reporting good health

- JPL requested that IV&V try to reproduce the repeated exception behavior

- Believed to be an OS issue in Task Control Block

- The ITC software environment would not recreate the ISI exception

- Moved VxWorks 6.4 image to RAD750 with test application

| 1111 | 11 | 11 | 11 | 11 | 1 | 1   | 11 | 1 | 11 | 1  | 1 | 1 | 11 | 1 | 1 | 11 | 1 | 1 | 1 | 1 | 11 | 1 | 1 | 1  | 11  |   |   |    |    |    |    |    |     |    |    |    |   |     |    |    |    |   |   |   |    |    |     |     |     |

|------|----|----|----|----|---|-----|----|---|----|----|---|---|----|---|---|----|---|---|---|---|----|---|---|----|-----|---|---|----|----|----|----|----|-----|----|----|----|---|-----|----|----|----|---|---|---|----|----|-----|-----|-----|

| 1111 | 11 |    | 11 | 11 | 1 | 1   | 11 | 1 | 11 | 1  | 1 | 1 | 1  | 1 | 1 | 11 | 1 | 1 | 1 | 1 | 11 | D | 1 | 1  | 1   |   |   |    |    |    |    |    |     |    |    |    |   |     |    |    |    |   |   |   |    |    |     |     |     |

|      | 1  | 11 | 11 | 11 | 1 | 1   | 11 |   |    | Ľ1 | 1 | 1 |    |   |   | 1  | 1 | 1 | 1 | 1 | 11 | ú | 1 | 1  |     |   |   |    |    | 1  | 1  |    |     |    |    |    |   |     |    |    | 11 | 1 | 1 |   |    |    |     |     | CR  |

| 1    |    | 11 | 11 | 11 | 1 | 1   | 1  |   | 11 | n  | 1 | 1 | 1  |   |   |    | 1 | 1 | 1 | 1 | 11 | n | 1 |    |     |   |   |    | 1  | n  |    |    |     |    |    |    |   |     |    |    | 11 | 1 | 1 |   |    |    |     |     |     |

| 11   |    | 1  | 11 | 11 | 1 | 1   |    | 1 | 11 | D  | 1 | 1 | h  |   |   |    |   |   |   |   | 11 |   |   |    |     |   |   |    | 11 |    |    |    |     |    |    |    |   |     |    |    | 11 |   |   |   |    |    |     |     |     |

| 111  |    |    | 11 | 11 | 1 |     | 1  |   |    | 1  | 1 | 1 |    | 1 |   |    |   |   |   |   |    |   |   |    | 1   |   |   |    |    |    | 1  | 11 | n   | 1  |    | 11 | 1 | 1   | 11 |    | 11 | 1 |   |   | 11 |    |     | 11  | 11  |

| 1111 |    |    | 1  | 11 |   |     | 11 |   |    |    |   |   | 1  |   |   |    |   |   |   |   |    |   |   |    | 11  |   | 1 | 1  | 11 | 11 | 1  |    |     | 1  |    |    |   |     | 11 |    | 11 |   |   | 1 | 1  |    | 1   | 11  | 1   |

| 1111 |    |    |    |    |   |     |    |   |    |    |   |   | n  |   |   | 1  |   |   |   |   |    |   |   |    | 11  |   |   |    |    |    |    |    |     | 1  |    | 11 |   | _   |    |    | 11 |   |   | 1 | 1  |    |     | 11  |     |

| 1111 |    |    |    |    |   |     |    | 1 |    |    |   |   |    |   |   | 'n |   |   |   |   | 1  |   |   |    | 11  |   |   |    |    | n  |    |    |     |    |    | 11 |   |     |    |    | 11 |   |   |   |    |    |     | 1   |     |

| 1111 |    |    |    |    |   |     |    |   |    |    |   |   |    |   |   | 11 |   |   |   |   |    |   |   |    | 11  |   |   |    |    | n  |    |    |     | ĩ  |    |    |   |     |    |    | 11 |   |   |   |    |    |     |     | 11  |

| 1111 | 11 |    |    | n  |   | 2.1 |    |   | 11 |    |   |   |    |   |   | 11 |   |   |   |   |    |   |   |    |     |   |   |    |    |    |    |    | h   | ï  |    | 11 |   |     |    |    | 11 |   |   |   |    |    | 15  | 11  | 2.2 |

| 1111 | 11 | 11 | 11 | 11 | 1 | 1   | 11 | n | 11 | 1  | 1 | 1 | n  | 1 | 1 | 11 | 1 | 1 |   |   |    |   |   |    |     |   |   |    |    |    |    |    |     |    |    |    |   |     |    |    |    |   |   |   |    |    |     |     |     |

| 1111 | 11 | 11 | 11 | 11 | 1 | 1   | 11 | 1 | 11 | ĥ  | i | ī | h  | 1 | 1 | 11 | 1 |   |   |   |    |   |   | De | eù  | e | h | 01 |    | 1e | m  | ŧ  | s   | us | et | er | 8 |     |    |    |    |   |   |   |    |    |     |     |     |

| 1111 | 11 | 11 | 11 | 11 | ñ | i   | 11 | n | 11 | 'n | ĩ | ī | n  | i | 1 | n  |   |   |   |   |    |   |   |    |     |   |   | 1  |    |    |    |    |     |    |    |    |   |     |    |    |    |   |   |   |    |    |     |     |     |

| 1111 | 11 | n  | ii | 11 | 1 | i   | 11 | i | 1  | ĥ  | i | ī | 1  | i | 1 | 1  |   |   |   |   |    | U | × | Ы  | nr  | k | s |    | Je | m  | s  | ic | m   | 5  | ί. | 5  |   |     |    |    |    |   |   |   |    |    |     |     |     |

| 1111 | 11 | 11 | 11 | 11 | ñ | 1   | 11 | n | 11 | ĥ  | ĩ | ĩ | n  | ñ | 1 |    |   |   |   |   |    |   |   |    |     |   |   |    |    |    |    |    |     |    |    | n  | 2 | 6   |    |    |    |   |   |   |    |    |     |     |     |

| 1111 |    |    |    |    |   |     |    |   |    |    |   |   |    |   |   |    |   |   |   | 1 |    |   |   |    |     |   |   |    |    |    |    |    |     |    |    |    |   |     |    | 2  |    | ħ |   |   |    | 19 | 184 | 1-1 | 28  |

|      |    |    |    |    |   |     | 1  |   | 1  |    |   |   | 1  | 1 |   |    |   |   |   | 1 |    |   | r |    | • 9 |   |   |    |    |    | ۳. | 1  |     | -  |    | -  | ~ | 1   |    |    | 1  |   |   |   |    | -  |     |     |     |

|      |    |    |    |    |   |     |    |   |    |    |   |   |    |   |   |    |   |   | • |   |    |   | p | •  | P   | E |   | T  | i. | IM |    |    | n   | -  |    |    |   |     | ě  | 0  |    |   |   |   |    |    |     |     |     |

|      |    |    |    |    |   |     |    |   |    |    |   |   |    |   |   |    |   |   |   |   |    |   |   |    |     |   |   |    |    |    |    |    |     |    |    |    |   |     |    |    | rs |   |   |   |    | 2  |     |     |     |

|      |    |    |    |    |   |     |    |   |    |    |   |   |    |   |   |    |   |   |   |   |    |   |   |    |     |   |   |    |    |    |    |    |     |    |    |    |   | ) F | ~  | e. | 13 | - |   |   |    | ~  |     |     |     |

|      |    |    |    |    |   |     |    |   |    |    |   |   |    |   |   |    |   |   |   |   |    |   |   |    |     | p | e |    | h  | m  | в. | -" | ••• | mr | ٩_ | EN | n |     |    |    |    |   |   |   |    |    |     |     |     |

|      |    |    |    |    |   |     |    |   |    |    |   |   |    |   |   | H  | Ш | в |   |   | Re |   |   |    |     |   |   |    |    |    |    |    |     |    |    | -1 |   |     |    |    |    |   |   |   |    |    |     |     |     |

- Through specific manipulation of the VxWorks Task Control Block, ITC was able to achieve a cyclic ISI behavior on the RAD750 target

- This information was conveyed back to the contractor so they could focus their analysis

- Ultimately the project determined the fault to be a "fluke" and no corrective action was taken

- There are many tools and methods required to provide successful software IV&V

- Static analysis and Dynamic analysis with software models are major players

- However, there will always be cases where flight equivalent hardware is needed to validate and verify specific software behaviors and anomalies

#### **Contact Information**

- Web Page

- <u>http://www.nasa.gov/centers/ivv/jstar/JSTAR.html</u>

- E-Mail

- Justin.R.Morris@nasa.gov

- Contact us for...

- Demonstrations of test beds

- Middleware usage agreements

- Simulator development

- Hardware modeling

- V&V Services, HWIL Testing, Performance Testing